# A-class Amplifier with FPPA as a Predictive Supply Voltage Control

### György Györök

Budapest Tech, Regional Education and Innovation Center H-8000 Székesfehérvár, Budai Str. 45

Hungary

gyorok.gyorgy@roik.bmf.hu

Abstract: A number so electro technique application exists, where it A-class regulation, control, or a circuit bias even only necessary. Circuit technique criteria like this, AB-, or C-class compared with applications the smaller sign distortion, more lineal transfer, bigger bandwidth, in a frequency range behavior. Together with this, we know it, that it A-class the dissipated power of a circuit technique passed on active device the largest, his efficacy the worst. Beside the correction of two latter parameters, the keeping of the benefits, energy yields a saving, and it increases the life expectancy of active device. To this using is a quite unusual mode of operation, programmable analog electronic circuit.

Keywords: Field Programmable Analog Array, predictive control, pulse width modulation

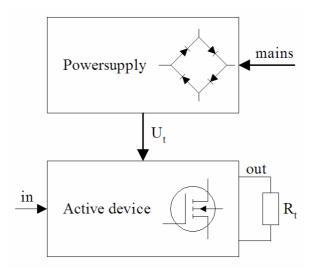

### **1** The traditional *A*-class setting

At the traditional *A*-class settings (figure 1.) the definition of the optimal biaspoint of the active device, the very important feature defining the performance relations significantly. The dissipation power of active device in this case as the product of the current and the voltages of there (1,2). This value is the largest ones, when the output resistor is the half voltage for the full supply voltage.

$$P_{out} = \frac{U_{out}^{2}}{R_{t}},\tag{1}$$

$$P_{dev} = \frac{(U_t - U_{out})^2}{R_d},$$

(2)

Figure 1 The traditional A-class setting

where  $U_{out}$  is the voltage of output,  $U_t$  is the voltage of power supply,  $P_{out}$  is the power of the load,  $R_t$  is the resistance of load,  $R_t$  is the resistance of semiconductor (for example  $R_{DS}$  of FET, at saturation).

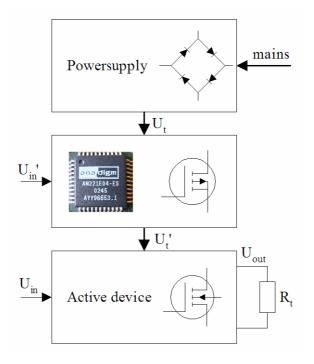

## 2 The novel A-class setting

Onto the minimization of this or his reduction we suggest the procedure when we modify it dynamically in the function of the control signal *A*-class his strengthening supply voltage. (Figure 2.) The AC voltage (mains) is arriving from the power network after rectifying and filtering we get  $U_t$ . The pulse width modulation (PWM) policy settling value of  $U_t$ ' in the output of this takes it to the necessaries voltage for de driving of  $R_t$ . The necessary means that it is active device here taking his characteristics into consideration, for it not let us not approach his nonlinearity. Of course to the correct function of the PWM controller, the production of the  $U_t$ ' voltage we need time. The equal 3 shows how can generate the predictive control signal.

$$U_{in}'(t) = U_{in}(t+\delta), \qquad (3)$$

where:  $\delta$  is the necessaries time for the working of control electronic.

Figure 2 The modified A-class control

Therefore  $U_{in}$  is a really stochastic signal not able to generate prediction control signal from there. So we change of both function, we delayed the *A*-class unit drive signal, and promptly controlled the PWM unit, as the writes the equal 4.

$$U_{in}(t) = U_{in}'(t-\delta), \qquad (4)$$

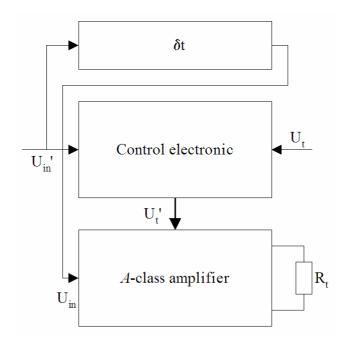

So the proposed equipment consists of three basic units (figure 3.): traditional *A*class amplifier, PWM control electronic, and a non-distortion delay line. The last one very easy can to realization in the practice, enough then we thing for the digital form storage information. In this case we need two DAC and one data pipeline like shift register.

The value of  $U_t$  depends of the input signal ( $U_{in}$ ) and constant (*Ud*). In the equal 5 the *k* is a multiply factor.

Figure 3 The block schema of proposed solution

$$U_{t}'(t) = k \int_{0}^{t} |U_{in}|' dt + Ud , \qquad (5)$$

The value of the dissipation calculable from (6)

$$P_{dev} = \frac{Ud^2}{R_{dev}},\tag{6}$$

where:  $P_{dev}$  is dissipation of active device,  $R_{dev}$  resistance of active device.

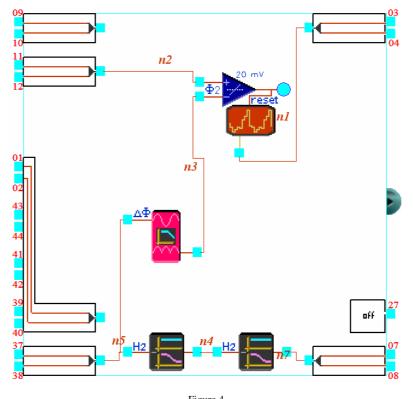

# **3** Realization with FPAA

To implement the above mentioned tasks, an excellent possibility is given by the use of the field programmable analog array (FPAA) as an universal circuit. In this case such a circuit can be implemented in which a FPAA circuit. In figure (4.) an AN221E04 type of FPAA integrated circuit inside is shown [13] [14] [15] [16]

Figure 4 Control circuit and delay line in FPAA

[17]. These circuits being programmed via digital surface form analogous circuit topology together with the likewise programmable determined circuit parameters. As a consequence, they can be favorably used to create different functional units [18] [19].

On the figure 4 seen the control circuit and delay-line. The  $pin_{37-38}$  connect to the  $U_{in}$ ' signal. Between the  $n_5$ - $n_7$  nodes are two all pass filter, with constant delay time. The  $pin_{07-08}$  gives the A-class amplifier the  $U_{in}$  signal. In other branch the input signal connects to de rectifier and low pass filter. The signal of  $n_2$  resets the base generator of PWM. On the  $pin_{03-04}$  we get the PWM impulses. The output of FPAA can drive directly a high power FET. From the Ut' connects a feedback to inner PWM generator reset function trough  $pin_{11-12}$ .

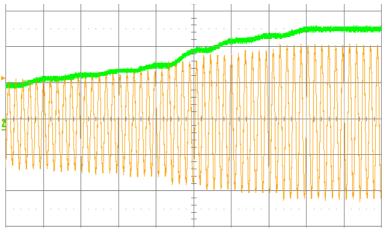

On the figure (5.) the current value of the supply voltage visible, in the function of the input signal.

A most interesting example of application when we use an electron tube triode with big current, in a new mode of operation strengthening when the leave is a cathode follower with the leaving of an output transformer suggested many times nowadays. In this case the supply voltage of the electron tube with 300-400V anode voltage, while a desired current flowing through  $16\Omega$  loudspeakers is greatness about with a value of 1A. Easily reasonable, that the electron tube transit dissipation some 150-200W. This not only because of that problem, when the *A*-class unnecessary big power dissipates, but because it is necessary to ensure the cooling separately and naturally the damage of the electron tube significantly, accelerates up.

Figure 5 Input signal (U<sub>in</sub>'), and U<sub>t</sub>' (upper)

#### Conclusions

With the help of the proposed procedure can be kept the benefit of the A-class technique with a switching mode got it united energy with an efficient regulation. The few milliseconds of retardation is the disadvantage of the procedure. Additional benefit means from the procedure when the controlled electronic circuit accomplishes the desired control characteristics collaborating with an embedded microcontroller.

#### References

- P. Andersen: Evolvable hardware artifical evolution of hardware circuits in simulation and reality. Department of Computer Science, University of Aarhus, Thesis, 1998.

- [2] C. C. Antini, R. Zebulum, M. A. C. Pacheco, M. M. R. Vellasco, and M. H. Szwarcman: Evolvable hardware, 2001. proceedings. The Third NAS DoD Workshop, 2001.

- [3] J. M. Birkner and H-T. Chua: Programmable array logic circuit. US Patent, 1970.

- [4] A. S. Deese and C. O. Nwankpa: Circuit theoretical analysis of reconfigurable analog load emulation circuit. http://www.ewh.ieee.org/conf/powertech.

- [5] S. Hauck: The future of reconfigurable systems. http://www.ee.washington. edu/people/faculty/hauck/publications/ReconfigFuture.PDF.

- [6] R. Kastner, A. Kaplan, and M. Sarrafzadeh: Synthesis Techniques and Optimizations for Reconfigurable Systems. Kluwer Academic Pub, 2003.

- [7] R. S. Muller and T. I. Kamins: Device Electronics for Integrated Circuits. John Wiley and Sons, 1986.

- [8] C. Reiser: Optimization of performance of dynamically reconfigurable mixed-signal hardware using field programmable analog array (FPAA) technology. PhD thesis, (1998).

- [9] F. Scott, L. Kemper, S. Afreen, and O.L. Weck: Flexible and reconfigurable systems: Nomenclature and review. In Proceedings of the ASME 2007 International Design Engineering Technical Conferences Computers and Information in Engineering Conference, volume IDETC/CIE, 2007, Las Vegas, Nevada, USA.

- [10] H. Scott: The future of reconfigurable systems. In Proceedings of 5th Canadian Conference on Field Programmable Devices, Montreal, June 1998 The Future of Reconfigurable Systems, volume IDETC/CIE, 1998, LEvanston, IL 60208-3118 USA.

- [11] Anadigm the dpASP Company: Dinamically programmable analog signal processing. <u>http://www.anadigm.com/</u>.

- [12] S. Zebulum, R, A. Stice, and K. Didier: The design process of an evolutionary oriented reconfigurable architecture. www.coe.uncc.edu/ kdatta/papers/The/20Design/20Process/200...urable/20Architecture.pdf.

- [13] Gy. Györök: Self Organizing Analogue Circuit by Monte Carlo Method. LINDI 2007 International Symposium on Logistics and Industrial Informatics September 13-15, 2007 Wildau, Germany, ISBN 1-4244-1441-5, IEEE Catalog Number 07EX1864C, Library of Congress 2007930060, p. 34–37.

- [14] Gy. Györök: Functional and Parametrical Self Adjustment in Analog Circuit. SISY 2007 5th International Symposium on Intelligent Systems and Informatics August 24-25, 2007 Subotica, Serbia, ISBN 1-4244-1443-1, IEEE Catalog Number 07EX1865C, Library of Congress 2007930059, p. 67–70.

- [15] Gy. Györök: Programmable Analog Circuit in Reconfigurable Systems. 5th Slovakien –Hungarien Joint Symposium on Applied Machine Intelligence, 2007 January 25-26, Poprad, Slovakia, ISBN 978-963-7154-56-0, p. 151– 156.

- [16] Gy. Györök: Self Configuration Analog Circuit by FPAA. 4th Slovakien Hungarien Joint Symposium on Applied Machine Intelligence, 2006 January 20-21, Herlany, Slovakia, ISBN 963 7154 44 4 p. 34–37.

- [17] Gy. Györök: The function-controlled input for the IN CIRCUIT equipment. IEEE-INES2004 Intelligent, Engineering Systems Conference, Cluj-Napoca, Romania, 2004 September 19-21, INES 2004, ISBN 973- 662-120-0, p. 443–446.

- [18] Gy. Györök. M. Makó: Self configuration Analog Circuits. XVIIth Kand conference 2006 "In memoriam Klmn Kand" Budapest Tech Kand Klmn Faculty of Electrical Engineering, 12-14 January 2006, ISBN 963 7154 426.

- [19] Gy. Györök, M. Makó: Acoustic Noise Elimination by FPAA. 3rd Romanien –Hungarien Joint Symposium on Applied Computational Intelligence, 2006 May 25-26, Timisoara, Romania, ISBN 963 7154 46 9, p. 571–577.

- [20] Gy. Györök: Reconfigurable Security Sensor by CCD Camera. 6th International Symposium of Hungarian Researches on Computational Intelligence, 2005 November 18-19, Buadapest, ISBN 963 7154 43 4, p. 585–588.

- [21] Gy. Györök, M. Makó: Configuration of EEG Input-unit by Electric Circuit Evolution. INES 2005, 9th International Conference on Intelligent Engineering Systems, 2005 September 16-19, 2005 Cruising on Mediterranean Sea, ISBN 0-7803-9474-7, IEEE 05EX1202C.

- [22] Gy. Györök, M. Makó: Configuration of universal analog input-unit by electronic circuit evolution. 6th International Carpatian Control Conference, 24-27 May, 2005., Miskolc, Hungary, ISBN 963 661 644 2, p. 395– 400.