# **Professional, Configurable Development System** for Microcontroller, FPGA and its Application

### **Gábor Marton**

Széchenyi István University, Egyetem tér 1, H-9026 Győr, Hungary

### Timót Hidvégi

Széchenyi István University, Egyetem tér 1, H-9026 Győr, Hungary Budapest Tech, Bécsi út 96/B, H-1034 Budapest, Hungary hidvegi@rs1.szif.hu

Abstract: A configurable professional development system and its application can be seen in this paper. The application is a programmable Final State Machine (FSM). The FSM can be used in the neural networks.

Keywords: Neural Networks, FPGA, PIC, FSM, Microcontroller

## **1** Introduction

Nowadays, the microcontrollers are very widespread devices, on one hand because they can be programmed easily, and on the other hand because they have a wide range of peripheral uses. A development system is essential for the improvement of these circuits. The development accessories are the PC and programmer, and testing circuit. The microcontroller manufacturers certainly produce testers and programmers for their products. But I have observed a problem. Whereas the developmental projects require different microcontrollers, the designers often need a new development system if they want to get in another development kit. That's why an idea has come up to my mind: I have to create an effective, configurational development system - my system applied a processor card in order to change over from one microcontroller system to another system.

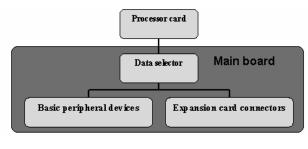

I found absolutely necessary to make a modular, configurational unit which is proper to have many different applications by attaching some type of external peripheral devices. The diagram of this development system is below: G. Marton *et al.* Professional, Configurable Development System for Microcontroller, FPGA and its Application

Figure 1 The development system diagram

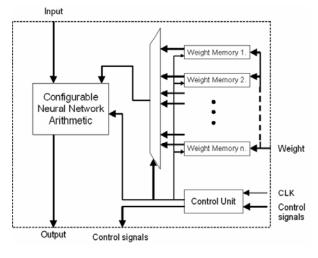

Figure 2 shows an architecture of a configurable neural network. The configurable neural network [1], [2], [3], [4] is built of configurable arithmetic core, control unit, multiplexer, and other memories.

Figure 2 Architecture of the configurable neural network

The control unit is a configurable Final State Machine.

In Section 2, the development system is presented. Section 3 is focusing on the application and its realization. The conclusions are given in Section 4.

## 2 The Development System

The Chapter shows the professional development system. The system is built of a processor card and a main board.

Magyar Kutatók 7. Nemzetközi Szimpóziuma 7<sup>th</sup> International Symposium of Hungarian Researchers on Computational Intelligence

### 2.1 The Processor Card

This unit includes the microcontroller. Its main duty is to make a connection between the pins of device and the connector. Beyond that, it includes the clock generator circuit and the connectors for the programming and the RESET unit as well.

The microcontrollers are like a computer, but they are integrated in one package. These ICs contain many peripheral devices, like CPU, I/O devices, A/D converters, timers and communication interfaces. For example: USART, I2C, SPI, CAN, USB.

The microcontrollers are RISC (Reducated Instruction Set Computer)-devices, and they are described as Harvard dual-bus architecture. My chosen unit is the PIC16F877, made by Microchip. This one is suitable to do 5 MIPS maximally.

The I/O ports are the most used devices. Due to the low number of I/O pins in the microcontrollers, the pins have to serve connection for more peripheral units, all at once. The way of data stream can be modified by the Trish bits of the register. If it is used for special data input, such as A/D converter, timer, PWM, then other register bits have to be modified too.

#### 2.2 Main Board

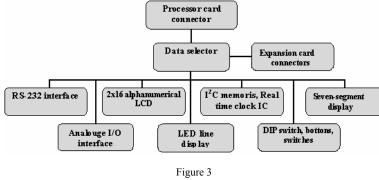

My development unit is based on its main board. The processor card connects to the main board, and we can select the way of data stream here (that is which devices or peripherals can be used). The schematic of this main board contains many basic peripheral devices, which are absolutely necessary for the development. Its diagram can be found below:

The main board block diagram

The function of expansion card modules becomes more important if we need special devices. That is why we need more input or output units, so I developed a

G. Marton *et al.* Professional, Configurable Development System for Microcontroller, FPGA and its Application

DIP switch board and a push-button extension unit. We usually wish to analyze the status of ports, so I have made a LED line display for this unit.

Nowadays, the RS-232 data transfer is not commonly used, so USB-based connection card becomes necessary due to its growing usage. This card contains an USB to parallel FIFO IC, made by FTDI.

## 3 An Application

A neural network controlled by a 'Final State Machine' programmed on PIC microcontroller [9] and a FPGA [10].

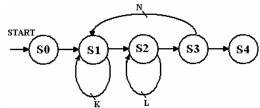

We have made a neural circuit in a Spartan III FPGA made by Xilinx. It is controlled by a PIC16F877-type microcontroller. My role was to make a 'Final State Machine' and its programming at my development system. Its graph can be found below:

Figure 4 Graph of the final state machine

The FSM is coded with assembly and VHDL. The Figure 5 shows the two programparts.

|          | MOVLW  | D'N-1' | ; N < 255  | WHEN   | WHEN s0 => state <= s1; |                      |

|----------|--------|--------|------------|--------|-------------------------|----------------------|

|          | MOVWE  | ТЗ     |            | WHEN   | 61 =>                   |                      |

| LABELO   | MOVLW  | D'K-1' | ; K < 255  |        | IF K = COUNT1 THEN      |                      |

|          | MOVWE  | T1     | 1449 00000 |        |                         | state <= s2;         |

|          | MOVLW  | D'L-1' | : L < 255  |        | ELSE                    |                      |

|          | MOVWE  | T2     |            |        |                         | state <= s1;         |

| LABEL1   | DECFSZ | T1.1   |            |        |                         | COUNT1 = COUNT1 + 1; |

|          | GOTO   | LABEL1 |            |        | END IF;                 |                      |

| LABEL2   | DECFSZ | T2,1   |            | WHEN : | HEN s2=>                |                      |

|          | GOTO   | LABEL2 |            |        | IF L = COUNT2 THEN      |                      |

|          | DECFSZ | T3,1   |            |        |                         | state <= s3;         |

|          | GOTO   | LABELO |            |        | ELSE                    |                      |

|          |        |        |            |        |                         | state <= s2;         |

|          |        |        |            |        |                         | COUNT2 = COUNT2 +1;  |

|          |        |        |            |        | END IF;                 |                      |

|          |        |        |            | WHEN : | 63=>                    |                      |

|          |        |        |            |        | IF N = CC               | UNT3 THEN            |

|          |        |        |            |        |                         | state <= s4;         |

|          |        |        |            |        | ELSE                    |                      |

|          |        |        |            |        |                         | state <= s1;         |

|          |        |        |            |        |                         | COUNT3 = COUNT3 + 1; |

|          |        |        |            |        | END IF;                 |                      |

| Figure 5 |        |        |            |        |                         |                      |

|          |        |        |            |        |                         |                      |

The assembly and VHDL programs

Magyar Kutatók 7. Nemzetközi Szimpóziuma 7<sup>th</sup> International Symposium of Hungarian Researchers on Computational Intelligence

#### Conclusions

Due to the nature of our project, we can not choose a wider collection of microcontrollers, so a programmable unit is essential. That is why we have developed a new processor card which is suitable for different types of CPLDs or FPGAs. The advantage of this device is based on its clock signal which is higher than any microcontrollers.

If it is used for automatic control, then we have to use outer expansion card(s) for surmount the differences of voltage level and power matching. Between these units a perfect discoupling must be built.

Of course, any expansion card can be made for my development system. My development system's basic advantage is the interchangeableness, so we can change from any processor card to any other one and many different expansion units can be attached to that one. By this, we can use many different functions based on the above described expansion units or we can complete the developed application as well.

#### References

- [1] P. Keresztes, Á. Zarándy, T. Roska, P. Szolgay, T. Bezák, T. Hidvégi, P. Jónás, A. Katona: An Emulated Digital CNN Implementation, *Journal of VLSI Signal Processing*, Special Issue: Spatiotemporal Signal Processing with Analogic CNN Visual Microprocessors, Vol. 23, No. 2/3, pp. 291-304, Kluwer, 1999

- [2] T. Hidvégi, P. Keresztes, P. Szolgay: Enhanced Modified Analized Emulated Digital CNN-UM (CASTLE) Arithmetic Cores, Journal of Circuits, Systems, and Computers, Special Issue on "CNN Technology and Visual Microprocessors, December 2003

- [3] T. Zeffer, T. Hidvégi: A Programmable Digital Cellular Neural Network Processing On- and Off-Chip Sensory Information, The 10<sup>th</sup> IEEE International Workshop on Cellular Neural Networks and their Applications, August 28-30, 2006, Istanbul, Turkey

- [4] T. Zeffer, T. Hidvégi: The Configurable Digital Cellular Neural Hopfield Network, INES 2006 10<sup>th</sup> IEEE International Conference on Intelligent Engineering Systems 2006, June 26-28, 2006, London, UK

- [5] Z. Nagy, P. Szolgay: An Emulated Digital CNN-UM Implementation on FPGA with Programmable Accuracy, DDECS'01 IEEE pp. 203-208, Győr, Hungary, April 18-20, 2001

- [6] P. Arató, T. Visegrády, I. Jankovits, Sz. Szigeti: High-Level Synthesis of Pipelined Datapaths, Edited by P. Arató, Panem Budapest, 2000

- [7] Enoch O. Hwang: Microprocessor Design, Principles and Practices with VHDL, Brooks/Cole 2004

G. Marton *et al.* Professional, Configurable Development System for Microcontroller, FPGA and its Application

- [8] F. Mayer-Lindenberg: Dedicated Digital Processors, Methods in Hardwae/Software System Design, John Wiley & Sons, 2004

- [9] www.microchip.com

- [10] www.xilinx.com